分析在 2017 年代号为 Naples 的 AMD 第一代 Epyc 处理器推出后不久,英特尔打趣说,其竞争对手已经沦为将一堆台式机芯片粘合在一起以保持相关性。

不幸的是,对于英特尔来说,这句话并没有完全过时,因为在短短几年后,这家 x86 巨头就开始伸手去摸胶水本身。

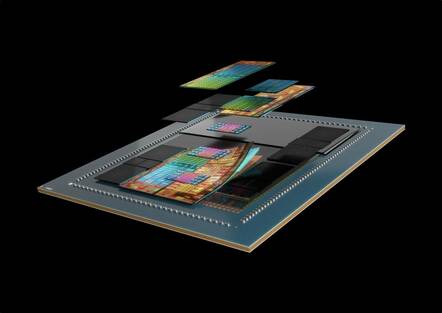

英特尔的至强 6 处理器于今年开始分阶段推出,代表了其第三代多晶粒至强处理器,也是其第一款采用异构小芯片架构的数据中心芯片,与 AMD 自己的架构类似。

虽然 Intel 最终看到了 AMD 小芯片战略的智慧,但它的方法却大不相同。

克服标线限制

为了快速回顾一下为什么这么多 CPU 设计正在从单片架构转向,这主要归结为两个因素:标线限制和良率。

一般来说,如果不在工艺技术方面进行重大改进,更多的内核必然意味着更多的硅。然而,模具实际可以达到的大小是有实际限制的 - 我们称之为标线极限 - 大约为 800 毫米2.一旦达到限制,继续扩展计算的唯一方法是使用更多芯片。

我们现在已经看到许多产品(不仅仅是 CPU)都实现了这一点,这些产品将两个大芯片塞进一个封装上。Gaudi 3、Nvidia 的 Blackwell 和 Intel 的 Emerald Rapids Xeon 只是其中的几个例子。

multi-die 的问题在于,它们之间的桥接通常是带宽方面的瓶颈,并且有可能引入额外的延迟。这通常不像将工作负载拆分到多个插槽那么糟糕,但这也是一些芯片设计人员喜欢使用较少数量的较大芯片来扩展计算的原因之一。

然而,更大的芯片的制造成本真的很高,因为芯片越大,缺陷率就越高。这使得使用大量较小的芯片成为一个有吸引力的提议,并解释了为什么 AMD 的设计使用了如此多的芯片——在最新的 Epycs 中高达 17 个。

有了这个入门知识,让我们深入研究 Intel 和 AMD 最新的 Xeon 和 Epyc 处理器的不同设计理念。

AMD 的老帽子

我们将从 AMD 的第 5 代 Epyc Turin 处理器开始。具体来说,我们正在研究该芯片的 128 核 Zen 5 变体,它具有 16 个 4 nm 内核复合芯片 (CCD),围绕着一个采用台积电 6nm 工艺技术制造的 I/O 芯片 (IOD)。

AMD 最新的 Epycs 包含多达 16 个计算芯片。

如果这听起来很熟悉,那是因为 AMD 在其第二代 Epyc 处理器中使用了相同的基本公式。作为参考,第一代 Epyc 缺少独特的 I/O 芯片。

正如我们之前提到的,使用大量较小的计算芯片意味着 AMD 可以获得更高的产量,但这也意味着它们可以在 Ryzen 和 Epyc 处理器之间共享芯片。

如果这些小芯片看起来很熟悉,那是因为 AMD 的 Epyc 和 Ryzen 处理器实际上共享相同的计算芯片。

此外,使用 16 核或 32 核 CCD,每个 CCD 具有 3 MB 的 L<> 缓存,在根据缓存和内存按比例扩展内核数量时,为 AMD 提供了额外的灵活性。

例如,如果您想要一个具有 16 个内核的 Epyc,由于许可限制,这是 HPC 工作负载的常见 SKU,那么实现这一目标的最明显方法是使用两个八核 CCD,这两个 CCD 之间具有 64 MB 的 L3 缓存。但是,您也可以使用 16 个 CCD,每个 CCD 都有一个活动内核,但板载缓存为 512 MB。现在这听起来可能很疯狂,但这两种芯片确实存在。

AMD 的第 5 代 Epycs 遵循熟悉的模式,即 16 个计算晶粒围绕一个中央 I/O 晶粒。

另一方面,I/O 芯片几乎负责除计算之外的所有工作,包括内存、安全性、PCIe、CXL 和其他 I/O(如 SATA),并且还充当芯片 CCD 和其他插槽之间通信的主干。

以下是 AMD Epyc Turin I/O 芯片的仔细研究。

将内存控制器放在 I/O 芯片上确实有一些优点和缺点。从好的方面来说,这意味着内存带宽在很大程度上独立于内核数量进行扩展。缺点是某些工作负载的内存和缓存访问延迟可能会更高。我们强调 “潜在” ,因为这种事情高度依赖于工作负载。

Xeon 的小芯片之旅

转向英特尔,这家芯片制造商的多晶片硅方法与 AMD 有很大不同。虽然现代至强处理器采用具有不同计算和 I/O 芯片的异构架构,但情况并非总是如此。

英特尔的第一款代号为 Sapphire Rapids 的多晶片至强处理器使用一个单片、中等内核数的晶片或四个极芯数晶粒,每个晶粒都有自己的内存控制器和 I/O。Emerald Rapids 遵循类似的模式,但为芯片的更高内核数 SKU 选择了两个更大的芯片。

如您所见,在 Sapphire 和 Emerald Rapids 之间,英特尔从四个中型芯片切换到一对几乎是 retical 的限量芯片。

所有这一切都在至强 6 中发生了变化,英特尔将 I/O、UPI 链路和加速器移到了一对在英特尔 7 工艺节点上制造的晶片上,该节点位于基于英特尔 3 构建的中心的一到三个计算晶片之间。

出于我们稍后会谈到的原因,我们将主要关注英特尔更主流的 Granite Rapids Xeon 6 处理器,而不是其多芯 Sierra Forest 部件。

看看 Intel 的计算芯片,我们看到了与 AMD 的第一个主要区别。每个计算块至少有 43 个板载内核,可以根据 SKU 进行融合。这意味着英特尔需要的芯片比 AMD 少得多才能实现 128 个内核,但由于面积更大,它确实有可能降低良率。

根据 SKU,Granite Rapids 使用夹在一对 I/O 晶片之间的一到三个计算晶片。

除了更多内核外,英特尔还选择将这些芯片的内存控制器放置在计算芯片本身上,每个芯片支持四个通道。从理论上讲,这应该会降低访问延迟,但这也意味着如果您想要所有 12 个 memory 通道,则需要填充所有三个 dies。

对于我们上个月查看的 6900P 系列部件,这不是你要担心的事情,因为每个 SKU 都有三个板载计算芯片。然而,这确实意味着 72 核版本只使用了封装上硅的一小部分。话又说回来,我们之前讨论的以 16 核 HPC 为中心的 Epyc 也是如此。

另一方面,英特尔的 6700P 系列部件将于明年初推出,根据所需的内存带宽和内核数量,将配备一个或两个计算芯片,这意味着高端内存将限制为 8 个通道,而在板载单个计算芯片的配置中可能只有四个通道。我们还对 HCC 和 LCC 芯片上的内存配置知之甚少,因此英特尔有可能加强了这些部件上的内存控制器。

就像 AMD 的 Epyc 一样,Intel 的 Xeon 现在也采用异构小芯片架构,带有计算和 I/O 芯片。

英特尔的 I/O 芯片也要窄一些,并包含 PCIe、CXL 和 UPI 链路的组合,用于与存储、外设和其他插槽进行通信。除此之外,我们还发现了大量用于 Direct Stream (DSA)、内存分析 (IAA)、加密/解密 (QAT) 和负载均衡的加速器。

我们被告知,在 I/O 芯片上放置加速器的部分原因是为了在数据流入和流出芯片时使它们更靠近数据。

英特尔、AMD 与科技巨头合作,对 x86 ISA 进行全面改造

AMD 将 Epyc 核心数量增加到 192,时钟频率高达 5 GHz,都灵首次亮相

凭借 Granite Rapids,英特尔又开始与 AMD 进行较量

AMD 淡化了爆炸半径扩大的风险,以及众核芯片的许可费用

我们该何去何从?

从表面上看,英特尔的下一代多芯处理器(代号为 Clearwater Forest)将于明年上半年推出,其模式与 Granite Rapids 类似,具有两个 I/O 芯片和三个计算块。

它可能看起来像一个缩小的 Granite Rapids,但显然这只是结构硅,下面隐藏了更多的小芯片。

然而,外表可能具有欺骗性。据我们了解,这三个计算芯片实际上只是隐藏着许多较小计算芯片的结构硅,这些芯片本身位于有源硅中介层的顶部。

根据今年早些时候 intel 展示的渲染图,Clearwater Forest 每个包最多可以使用 12 个计算芯片。硅中介层的使用绝非新鲜事物,它具有许多优势,包括更高的芯片到芯片带宽和比通常在有机衬底中看到的更低的延迟。这与英特尔最高内核数的 Sierra Forest 部件上的一对 144 核计算芯片大相径庭。

如果英特尔今年早些时候调侃的这个渲染图有什么值得推翻的,那么 Clearwater Forest 隐藏的小芯片比 Granite Rapids 多得多

当然,讨论将在 Clearwater 森林中使用的技术的效果图并不意味着这正是我们明年到达时会得到的。

也许更大的问题是 AMD 下一步将如何发展其小芯片架构。看看 AMD 的 128 核 Turin 处理器,封装上没有太多空间容纳更多硅,但 House of Zen 仍然有一些选择可供选择。

首先,AMD 可以简单地选择更大的封装,为额外的小芯片腾出空间。或者,芯片制造商也可以在更小的芯片上封装更多的内核。然而,我们怀疑 AMD 的第六代 Epycs 实际上最终看起来更像其 Instinct MI300 系列加速器。

MI300A 将 24 个 Zen 4 内核、3 个 CDNA 128 GPU 芯片和 3GB HBM<> 内存整合到一个封装中,旨在处理 HPC 工作负载

您可能还记得,与 MI300X GPU 一起推出的是一个 APU,它将芯片的两个 CDNA3 tiles 交换为三个 CCD,它们之间有 24 个 Zen 4 内核。这些计算块堆叠在四个 I/O 芯片上,并连接到一组 3 个 HBM<> 模块。

现在,这只是猜测,但不难想象 AMD 会做类似的事情,将所有内存和 GPU 芯片换成额外的 CCD。可以想象,这样的设计也将受益于更高的带宽和更低的 die-to-die 通信延迟。

这是否真的会发生,只有时间会证明一切。我们预计 AMD 的第 6 代 Epycs 要到 2026 年底才会到来。®